Nouveau développement SDR

Pour les radioamateurs qui comme moi souhaitent construire leurs transceivers pour les bandes V/U/SHF, il est clair que l'utilisation de modules SDR facilite grandement les choses et le concept de superhéthérodyne à double changement de fréquence ainsi des transverters classiques perd un peu d'attrait.

Beaucoup utilisent le modèle bien connu appelé « ADALM-Pluto » développé par Analog Devices autour du chip AD-9363 et d'un FPGA ZYNQ XC7Z010 ou XC7Z020.

Dans ce contexte, j'ai déjà réalisé des cartes d'extension pour ce Pluto et quelques clones identiques.

Voir : https://www.f1te.org/index.php/realisations/sdr/nouvelle-carte-dextension-pour-adalm-pluto

Comme ce concept « Pluto » semble avoir bien marché techniquement et donc commercialement, les clones de ce SDR Pluto fleurissent maintenant. Autour de 100 € nous pouvons trouver des modules permettant de réaliser des stations en particulier pour le trafic satellite, QO-100 ou les nombreux satellites défilants par exemple, permettant de trafiquer dans tous les modes y compris la DATV.

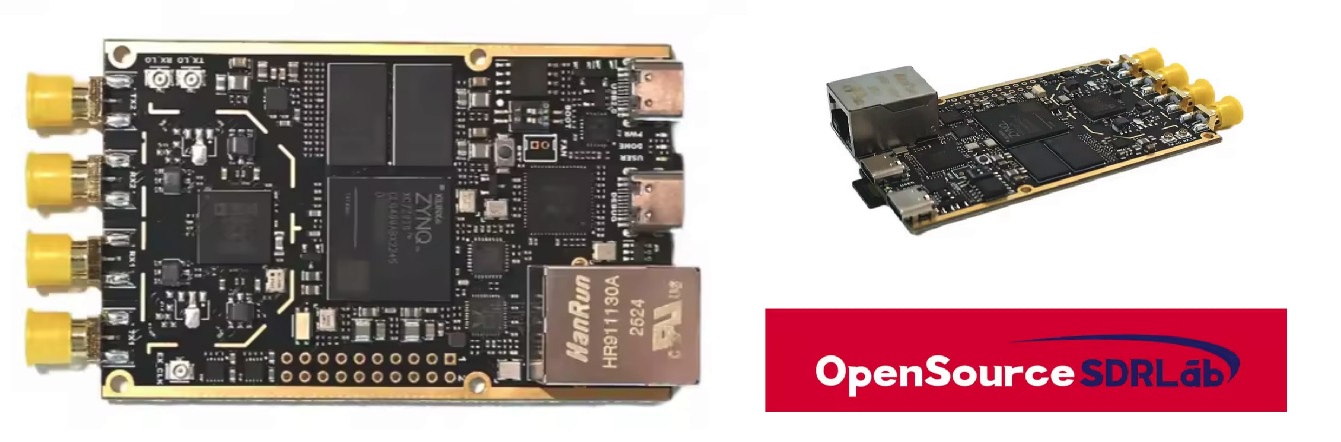

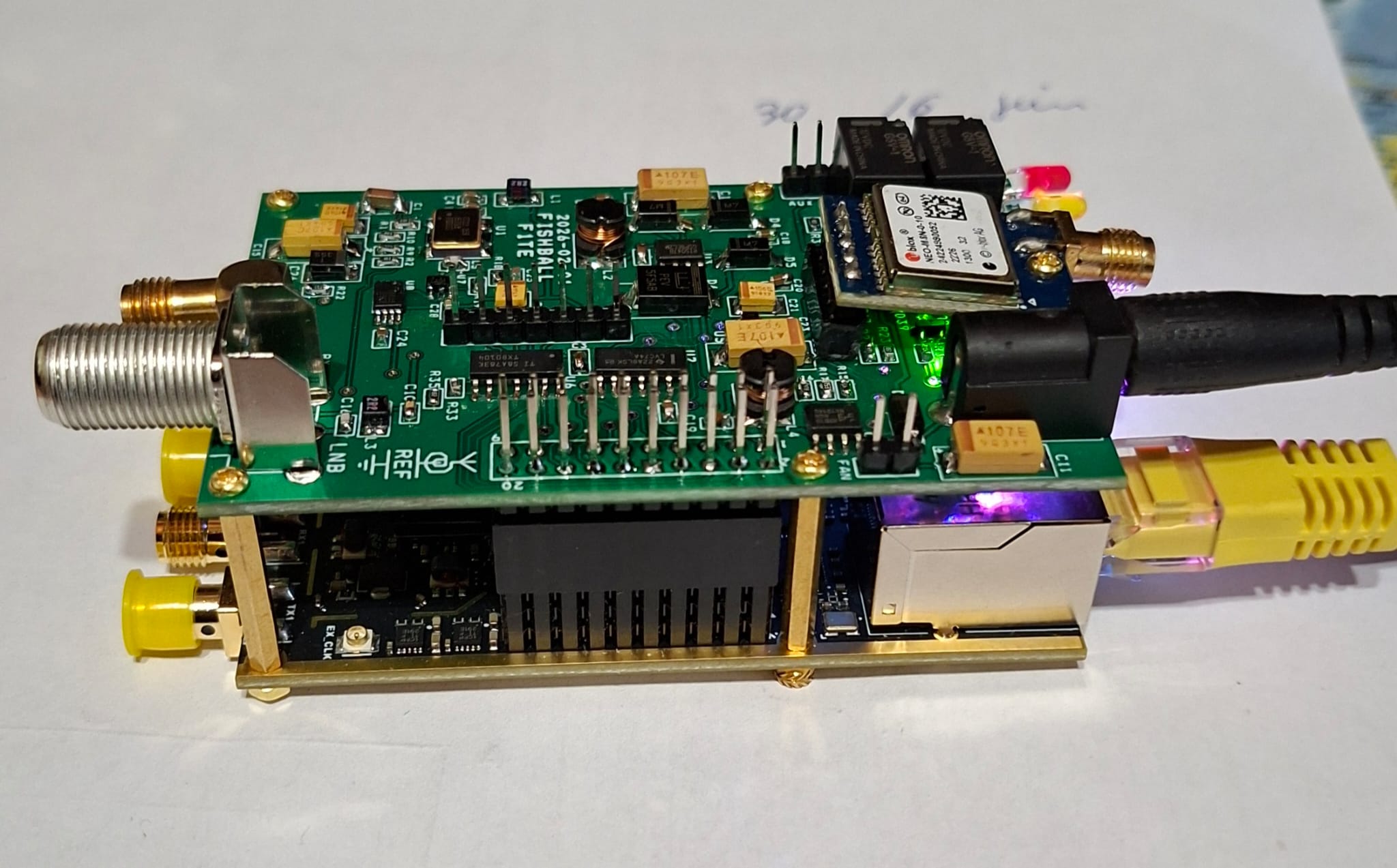

Figure 1: OpenSourceSDRLab édition professionnelle 7020 pour Pluto SDR

Ce SDR mesure 50x80 mm. Il dispose de deux E/S Rx-Tx et la communication vers le PC supportant l'interface de trafic (comme SDR-Console ou SDR-TVde G4ELI) se fait soit en USB de type C soit directement en Ethernet ce qui est une grosse nouveauté.

Il est également équipé d'un port de carte micro-SD pour pouvoir y installer un système complet (voir plus bas) sans avoir à reflasher le firmware.

En résumé considérer qu'il s'agit d'un RPi2 avec un SDR RX/TX performant en mode 'embarqué'.

J'ai choisi le modèle ZYNQ-7020 avec amplificateurs sur les sorties TX. Reste ensuite à rajouter les amplificateurs de puissance RF, adaptés aux fréquences utilisées.

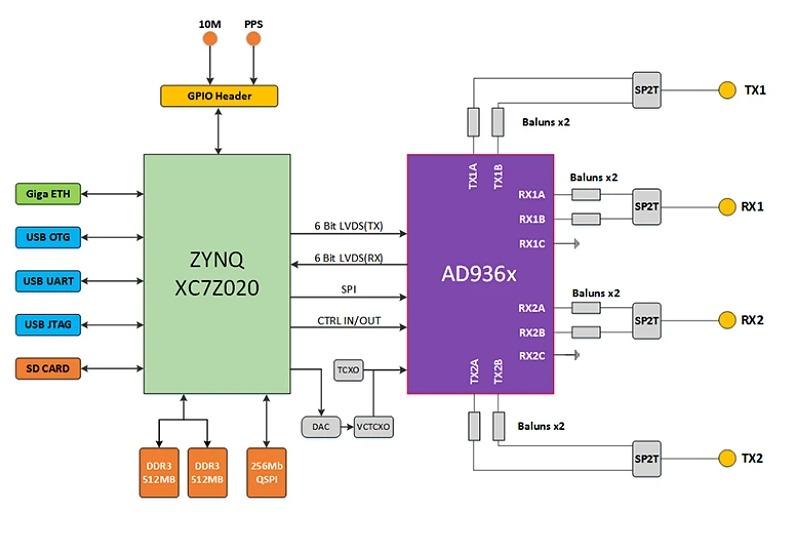

Figure 2: Bloc-diagramme

Je travaille donc sur une carte d’extension similaire pour ce SDR très intéressant, utilisant le même chip RF et un FPGA plus puissant ce qui permet de lui transférer des fonctions logiques que l'on câblait dans la version précédemment citée. Plus besoin de chips diviseurs logiques, comparateurs et autres fonction de reprogrammation du GPS, tout ceci est pris en compte dans le module SDR par son processeur et son FPGA.

Le rôle de cette carte d'extension est d'adjoindre à ce SDR les fonctions qui lui manquent pour la gestion du transceiver.

-

L'alimentation 5 V de la carte SDR

-

Une gestion d'un relais PTT.

-

La gestion d'un LNA/LNB en 13 ou 18 V, alimenté par le câble coaxial.

-

Générer une horloge pilotée GPS de façon à disposer de fréquences précises :

-

Une horloge (clock) à 40 MHz pour piloter le chip RF AD9363

-

Deux horloges (clock) de référence sur 10 et 25 MHz pour utilisations diverses.

Mais avant de parler du schéma de cette carte d'extension, posons quelques questions à ChatGPT dont je lui laisse l'entière responsabilité des réponses.

|

Qu'est ce qu'un AD9363 ?

L’AD9363 est un circuit intégré radiofréquence (RF) très utilisé dans les systèmes de communication sans fil et les radios définies par logiciel (SDR). Présentation L’AD9363 est un transceiver RF large bande fabriqué par Analog Devices. Caractéristiques principales

À quoi sert-il ? Il est utilisé dans :

Où le trouve-t-on ? On le retrouve notamment dans certaines plateformes SDR populaires comme :

En résumé : l’AD9363 est une puce RF polyvalente permettant d’émettre et recevoir des signaux radio sur une large gamme de fréquences, très utilisée pour le prototypage et les systèmes SDR. |

Qu'est que le ZYNQ XC7Z020 ?

Le Zynq XC7Z020 (souvent appelé Zynq-7020) est un composant électronique programmable qui combine un processeur et un FPGA dans une seule puce. Il est très utilisé dans les systèmes embarqués et les applications temps réel. Présentation Le Zynq-7020 fait partie de la famille Zynq-7000, développée par Xilinx (désormais intégré à AMD). Il s’agit d’un SoC FPGA (System on Chip + FPGA). Architecture : deux mondes dans une puce 1. Processing System (PS)

2. Programmable Logic (PL)

Le PS et le PL communiquent via des bus haute vitesse. Caractéristiques principales

À quoi sert-il ? On le retrouve dans :

Exemples de cartes utilisant le Zynq-7020

En résumé : le Zynq-7020 est une puce très puissante qui combine la flexibilité d’un FPGA et la simplicité d’un processeur ARM, idéale pour les systèmes embarqués avancés.

|

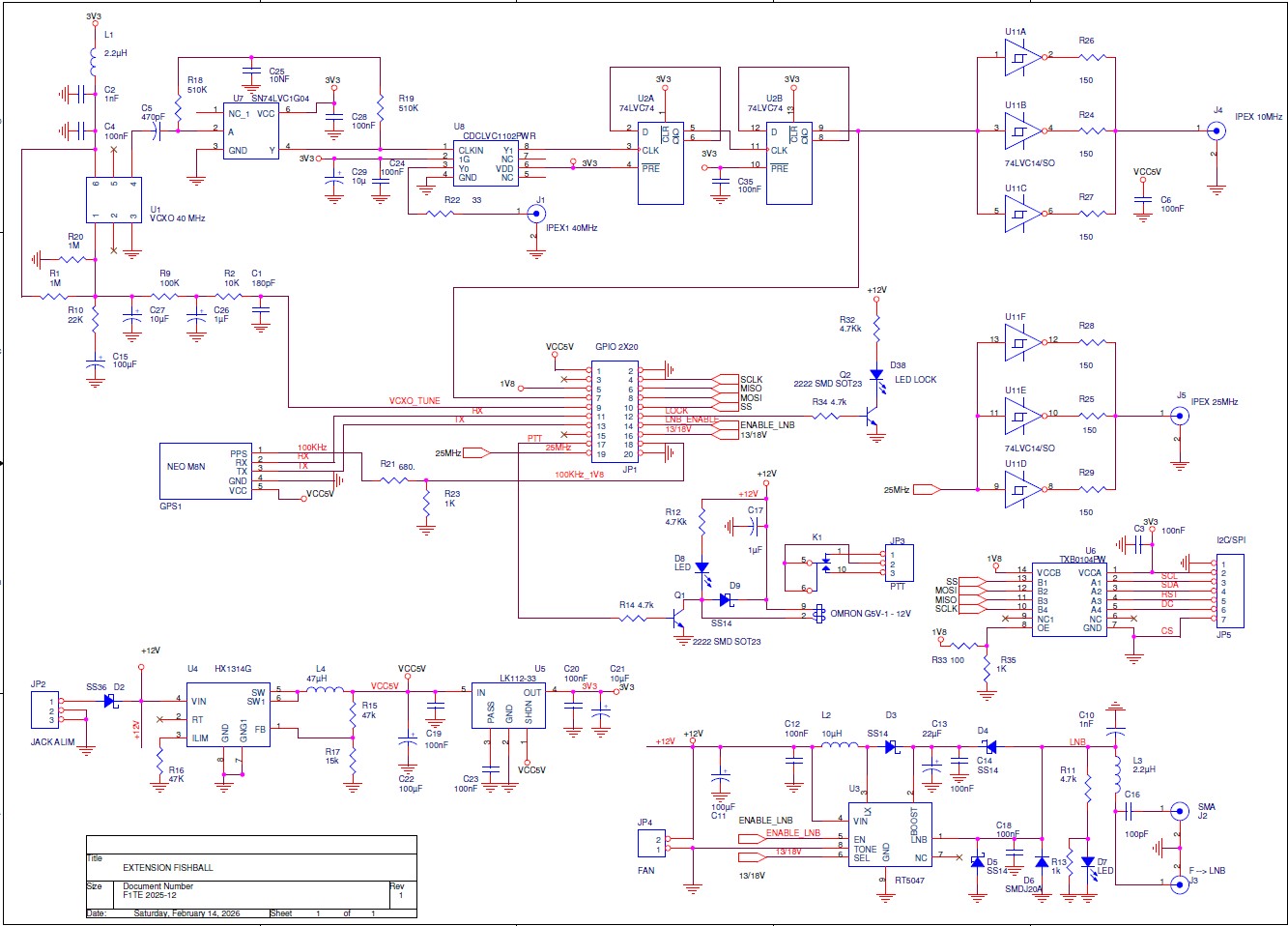

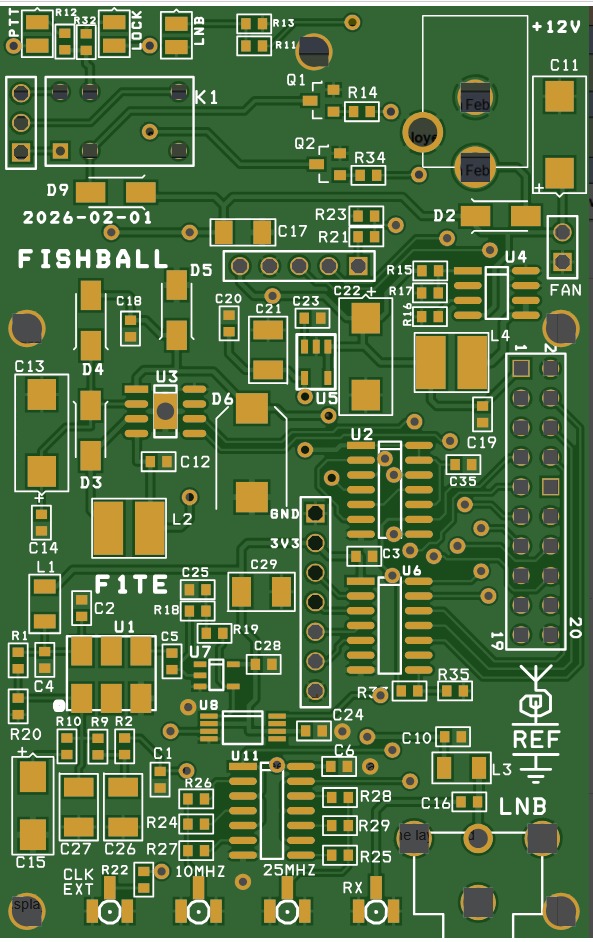

Ceci exposé, voici le schéma proposé pour cette carte d'extension spécifique à ce SDR.

Figure 3: Schéma

Nous trouvons :

-

Une alimentation 5 V à découpage et un régulateur 3,3 V,

-

Un générateur 13/18 V programmable commandé par les lignes du bus GPIO de la carte SDR.

-

Un VC-TCXO 40 MHz suivi de circuits buffers et d'un diviseur par 4 pour ne faire travailler le FPGA qu'à 10 MHz seulement.

-

La tension de commande du VC-TCXO est délivrée par le FPGA à la suite de la comparaison de phase entre le signal de référence fourni par le GPS et le signal 40

MHz venant du VC-TCXO. -

On trouve bien sûr un relais PTT et les drivers pour les signaux 10 MHz et 25 MHz.

-

Est présent sur la carte un driver de bus bidirectionnel pour disposer d'un bus I2C ou SPI, géré par le FPGA, en vue de la connexion de périphériques utilisant ces protocoles de communication.

Comme on peut le voir, les fonctions logiques sur la carte sont réduites au minimum et c'est le FPGA et le processeur inclus dans la carte SDR qui prennent maintenant en charge une grande partie de ce qui se faisait par hardware et par le software d'un Arduino dans la précédente carte d'extension.

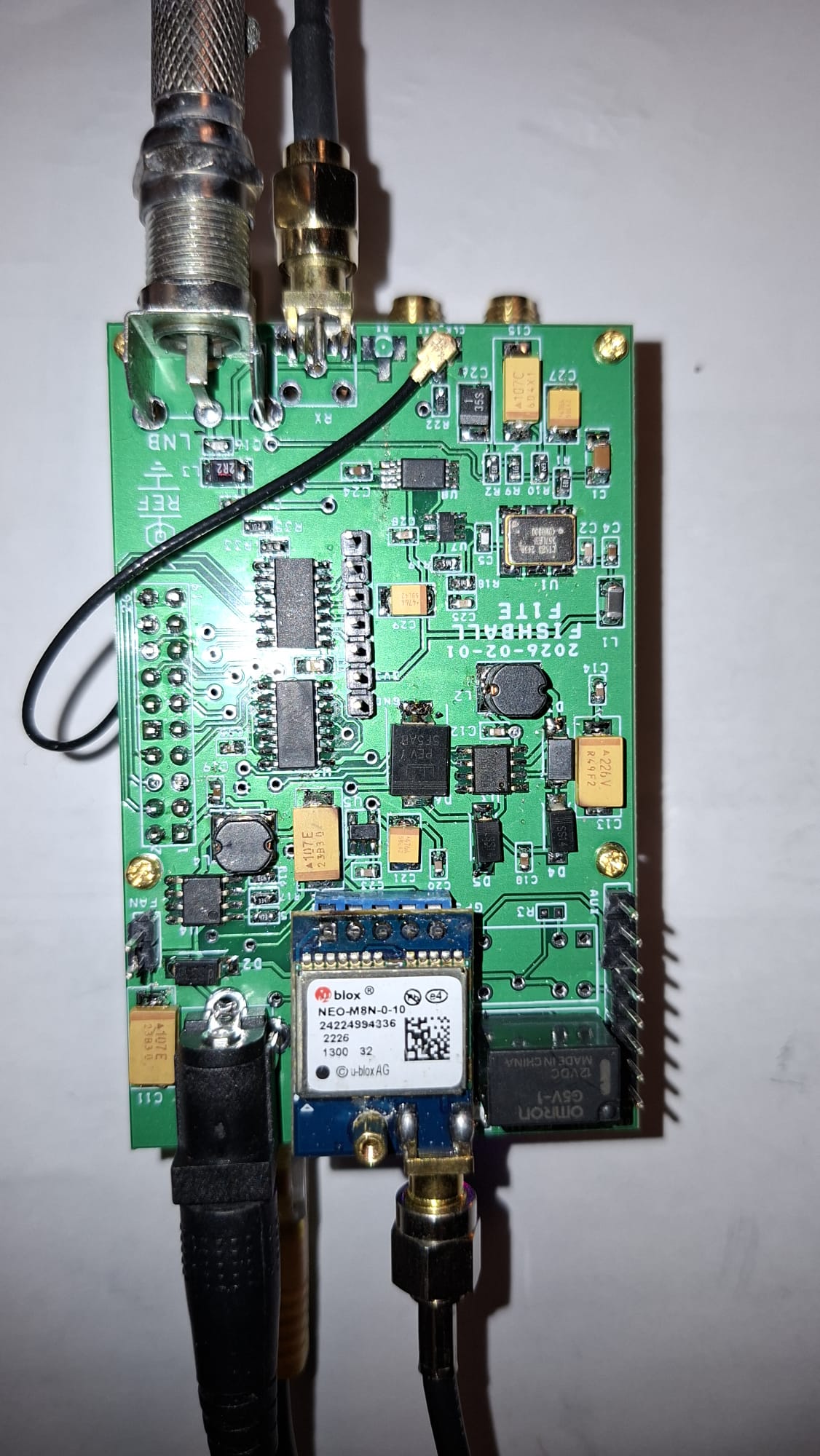

Figure 4, 5, 6: Prototypes

Bien sûr, tout le travail réside alors dans du développement software tant dans la compilation du modèle logique que devra exécuter le FPGA que dans les commandes à ensuite effectuer, pour gérer le PTT ou asservir le VC-TCXO. Mais pour cela nous avons un spécialiste, en la personne d'Évariste F5OEO, se chargeant de cette partie.

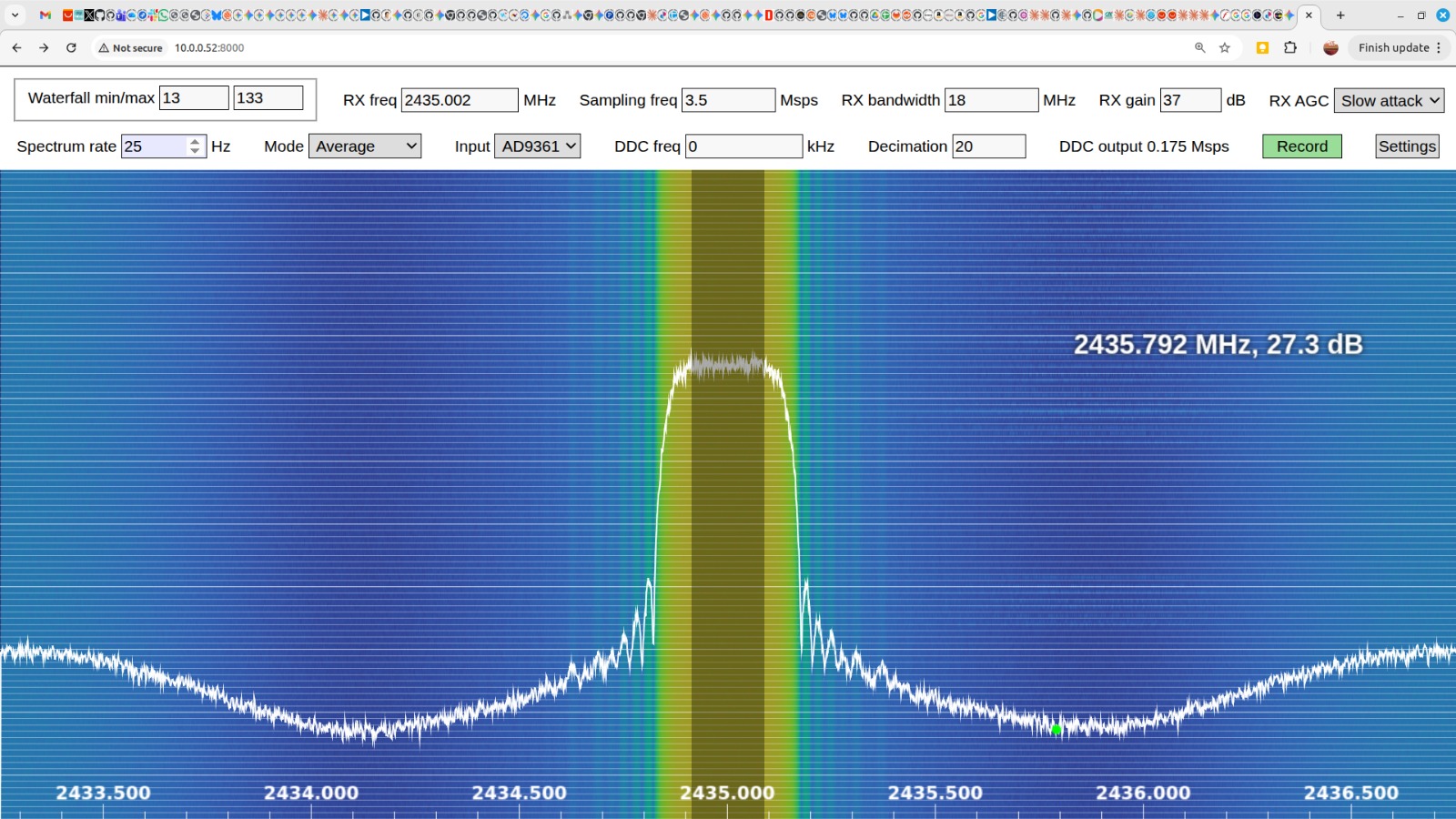

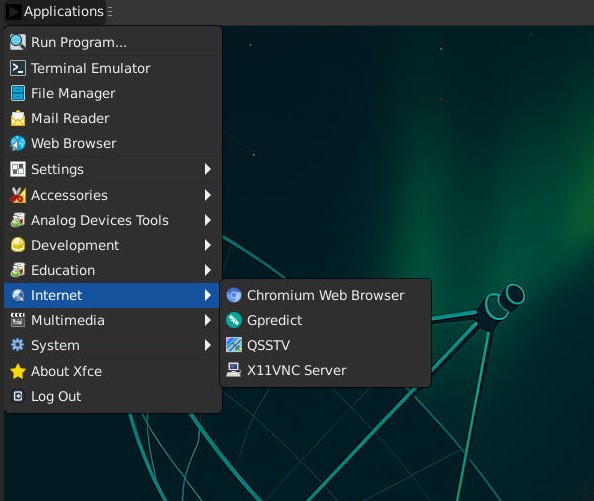

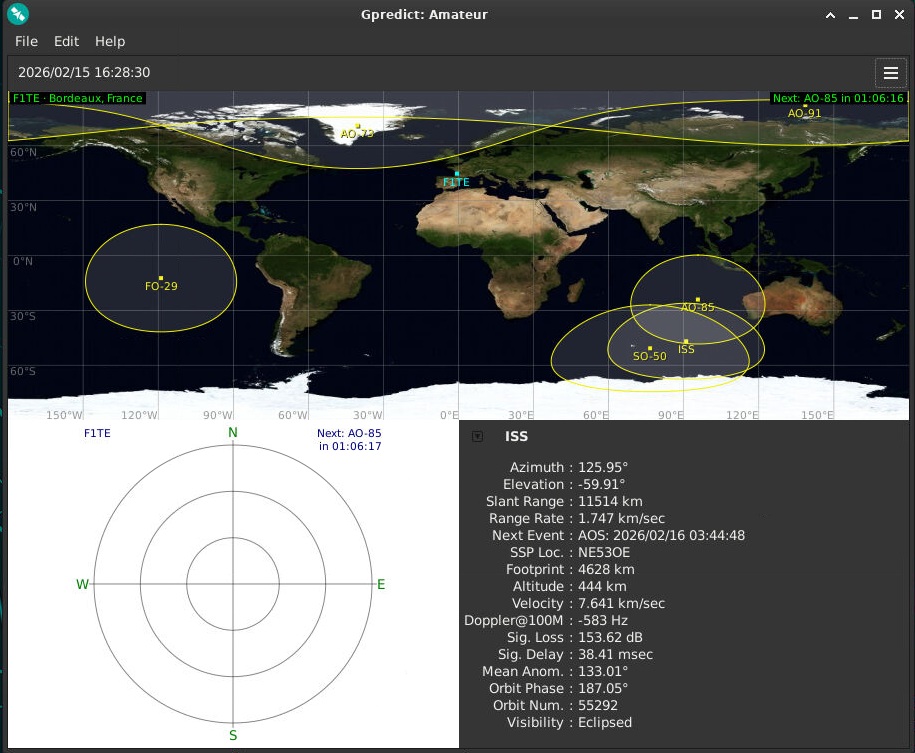

Au delà de la simple gestion radiofréquence SDR, une grande quantité de logiciels est embarquée dans ce FPGA et son processeur ARMv7 sous un Linux Debian. Vous y trouverez aussi un analyseur de spectre (maia-sdr), une version de Gpredict, des classiques comme rtl_433, readsb (aero, ADSB), dumpvdl2 (ACARS), luaradio et bien plus. Ces applications sont toutes accessibles avec un simple navigateur, mais nous reviendrons sur le sujet.

Figure 7: Vue du spectre au travers de maia-sdr (EA4GPZ) directement accessible en page web sur le port 8000. On peut visualiser 61 MHz de large d'un coup.

Figure 8: Le bureau "Zukaneoper" directement accessible en page web sur le port 6080.

Figure 9: Gpredict

Cet article n'est qu'une présentation du projet que nous menons Évariste et moi et nous aurons donc l'occasion d'en reparler.

N'hésitez pas à me faire part de vos remarques pour faire évoluer le projet.

73, Lucien F1TE

Bibliographie.

Présentation de F5OEO au FOSDEM 2026 à Bruxelle : https://fosdem.org/2026/